# 智能硬件体系结构 2025年秋季 作业1

截止日期: 2025/11/7 23:59

### 1、简单逻辑设计(30分)

- 1) 利用CMOS静态逻辑电路,实现:  $Y = \overline{A(BE+CD)+C} + \overline{E}(F+\overline{AD})$ ; 画出PDN和PUN组成的静态逻辑电路图。 (20分)

- 2) 简单讨论A、E两个信号的相对时序对以上逻辑电路的延迟影响,考虑以下情况: (10分)

- i) 如果A比E早到达;

- ii) 如果A比E晚到达。

### 2、布斯编码乘法 (30分)

使用Booth编码,对两个8-bit补码整型数进行乘法运算。

- 1) 利用Radix-8 Booth编码计算乘法:其中31为被乘数,-55为乘数,写出具体步骤(参考课程内容)。 (15分)

- 2) 利用Radix-16 Booth编码计算乘法: 其中31为被乘数,-55为乘数,写出具体步骤(参考课程内容), 并简要分析与前述Radix-8 Booth编码乘法在硬件电路实现上的优势和劣势。(15分)

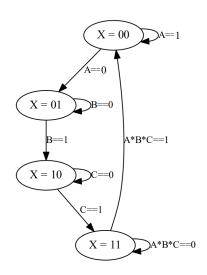

#### 3、有限状态机(20分)

针对以下有限状态, X为状态, A、B、C均为输入, 列出状态、输入转移表, 利用简单逻辑门画出该有限状态机的电路实现图, 参考课程讲义内容。(转移表: 10分; 电路图: 10分)

## 4、开放式问题 - 立方根计算硬件设计 (20分)

在课堂中,我们学习了如何设计加法器、乘法器、Winograd卷积加速核等。对于更复杂的逻辑功能,专用计算单元的设计变得尤为重要。假设某AI芯片公司需要设计输入X为32比特整型数(补码INT32)、输出Y为16比特浮点数(FP16 包含 1bit 符号位、5bit 指数位、10bit 尾数位)的立方根(Y =  $\sqrt[3]{X}$ )计算单元。简要说明如何利用数字逻辑电路进行立方根计算,并利用Python、C/C++、Matlab或其他代码进行硬件行为的比特级模拟仿真与验证,研究所设计的复杂计算单元输出结果与电脑软件参考输出的误差,并简单探讨减小计算误差的方法及其可能造成的硬件面积、速度代价。(清晰描述硬件设计思路:10分;完成行为级仿真:5分;简要分析减小计算误差方法:5分)